Korszerű rendszermodulok tápellátásának gyors tervezése

Megjelent: 2018. augusztus 13.

Azoknak a mérnököknek, akik programozható rendszermodulokat terveznek, rendszerint komoly támogatásra van szükségük a prototípus megtervezéséhez és üzembe helyezéséhez. Az Avnet rendszermodul (System-On-Module – SOM) koncepciója áthidalja a legalapvetőbb rendszerintegrációs problémákat, és egy – az Infineon által kimondottan a korszerű FPGA-k és programozható rendszercsipek számára kidolgozott – rugalmas energiamenedzsment-megoldással segíti a fejlesztőmérnökök munkáját.

Azoknak a mérnököknek, akik programozható rendszermodulokat terveznek, rendszerint komoly támogatásra van szükségük a prototípus megtervezéséhez és üzembe helyezéséhez. Az Avnet rendszermodul (System-On-Module – SOM) koncepciója áthidalja a legalapvetőbb rendszerintegrációs problémákat, és egy – az Infineon által kimondottan a korszerű FPGA-k és programozható rendszercsipek számára kidolgozott – rugalmas energiamenedzsment-megoldással segíti a fejlesztőmérnökök munkáját.

Bevezetés: Programozható rendszercsip-alkalmazások fejlesztése – repülőrajttal

A programozható rendszercsip (Programmable System-on-Chip – SoC) áramkörök segíthetnek az olyan új termékek fejlesztésének felgyorsításában, a készülékek széles választékának méret- és tápteljesítmény-felvétel csökkentésében, amelyeknél nagy számítási teljesítményre és rövid válaszidőkre van szükség. Ennek jellegzetes példái a jó minőségű motorhajtások vezérlése, a gépi látórendszerek és a gépi tanulásra képes megoldások fejlesztése. Ugyanakkor egy SoC-alapú rendszert működő állapotba hozni távolról sem egyszerű feladat, hiszen olyan összetett problémák megoldására kényszeríti a tervezőt, mint például a NyÁK-nyomvonaltervezés – különös tekintettel a nagy sebességű adatvezetékekre – a rendszermemória és az olyan interfészek integrálása, mint az ethernet és USB, vagy akár a tápellátásmenedzsment. Ezek közül az utóbbi egyre bonyolultabb feladattá válik a programozható rendszercsipek újabb és újabb generációinak megjelenésével, mivel ezekben több fontos rendszertulajdonság integrációja valósul meg, és egyre szigorúbbak a rendszerszintű követelmények.

1. ábra Az UltraZed-EG rendszermodul (SOM) felgyorsítja a nagy integráltságú, programozható rendszercsipekkel) történő fejlesztési munkát

Egy teljes beágyazott feldolgozó alrendszert tartalmazó, SoC-alapú rendszermodul segíthet a fejlesztőnek abban, hogy úrrá legyen a rendszer felépítése és hibakeresése során fellépő nehézségeken, és lehetővé teszi számukra, hogy gyorsan megvalósítsanak és futtassanak egy platformot, amellyel a rendszercsip konfigurálását gyakorlatilag egyidejűen lehet fejleszteni az alkalmazással. Az Avnet UltraZed™-EG SOM (1. ábra) és a hozzá kapcsolódó alkalmazásspecifikus hordozókártyákat tartalmazó referenciatervek úttörő szerepet vállaltak a programozható rendszercsipek alkalmazásainak fejlesztésében. Azáltal, hogy a rendszermodult a hordozókártyához csatlakoztatják, olyan használatra kész hardverplatformra tesznek szert, amely jelentősen, akár 50%-kal is lerövidítheti a rendszer megvalósításához és hibamentesítéséhez szükséges időt.

A rendszermodul egy Xilinx Zynq® Ultrascale™+ XCZU3EG multiprocesszoros rendszercsipet (MultiProcessor SoC – MPSoC) tartalmaz. Ez az eszköz a nagy integráltságú, nagy teljesítőképességű programozható rendszercsipek tipikus példája, amely egy korszerű FPGA-részegységet egyesít egy többmagos feldolgozó alrendszerrel, egy nagy sebességű rendszermemóriával és több gigabit/s sávszélességű kommunikációs interfészekkel. Azonban akár egy olyan rendszermodult használnak, mint az Avnet UltraZed-EG, akár egy hagyományos FPGA-alapú prototípuskártyát, ezeknek a különféle eszközöknek a megfelelő tápellátását megvalósítani számos kihívással szembesíti a fejlesztőt.

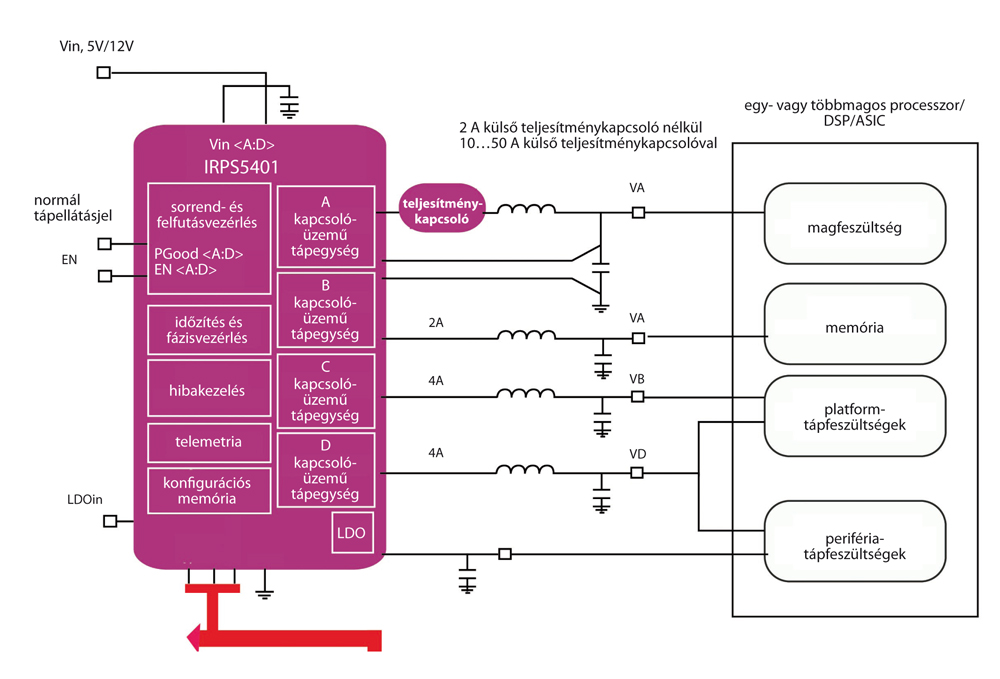

2. ábra IRPS5401 IC-vel felépített mintaáramkör programozható SoC feldolgozó alrendszer tápellátására

A tápellátás kihívásai

A jelenkor programozható SoC-eszközei többféle, különböző feszültségű tápellátó bemenettel rendelkeznek. A rendszermag tápfeszültségén kívül a Zynq feldolgozórendszerekben külön tápfeszültség-tartományok szolgálnak az integrált memória, a be- és kimeneti egységek (I/O), a fázisszinkronizált alegységek (Phase Locked Loop – PLL), és a több gigabit/s sávszélességű soros adóvevő áramkörök (SerDes[1]) tápellátására. Az eszköz használható „állandóan bekapcsolt” üzemmódban éppúgy, mint energiatakarékos üzemmódban – ugyanakkor ezek különféle fajtái szintén szükségessé tehetnek további tápsíneket, amelyek szintén befolyásolják a tápegység tervezését.

A felhasznált eszköz típusától függően 7 és 10 közé tehető a szükséges, független tápfeszültségsínek száma, és ezeket a síneket egy előírt sorrendben kell be-, illetve kikapcsolni. Az Infineon – a Xilinx céggel együttműködve – kidolgozott és forgalomba hozott olyan optimalizált tápfeszültség-menedzselő eszközöket, amelyek a Xilinx Zynq UltraScale+ sorozat Zu02…Zu19 tagjai számára kínálnak megoldásokat. Ezek leírása az [1] és [2] dokumentumokban található az alábbi fejezetekben: „Always On: Cost Optimized Power Rail Consolidation” és „Always On: Power/Efficiency Rail Consolidation for Low Power Devices”. Az Infineon megoldásait alkalmazták néhány referenciatervben, amelyet az Avnet és a Xilinx tervezett a Zynq UltraScale+ termékcsaládhoz.

Pontos specifikációk léteznek az egyenfeszültségszintek pontosságára és az ugrásszerű terhelésváltozásra adott válaszfüggvényre. A Zynq UltraScale™+ MPSOC magfeszültségének megkívánt pontossága 1%, és a feszültség hullámosságának maximális értéke 10 mVp-p. Továbbá, mivel a szóban forgó eszközöket olyan korszerű eljárásokkal készítik, mint a Xilinx 16 nm-es FinFET technológiája, ezt a nagy pontosságot még a rendkívül alacsony, 0,72 V-os névleges értéknél is biztosítani kell. Ráadásul az olyan váltakozóáramú specifikációkra, jelesül az ugrásszerűen változó terhelésre adott válaszfüggvényre nézve különlegesen szigorú követelményeknek kell eleget tenni. A Xilinx előírja, hogy a túllövésnek és alullendülésnek a névleges érték 3%-án belül kell maradnia, akár a terhelőáram 30%-os, ugrásszerű változása esetén is. Az olyan, kisebb eszközöknél, mint a ZU02…ZU05 eszközcsaládok tagjai, a csúcsáram 7…16 A között mozog, míg a nagyméretű Zynq MPSoC-ok, mint a ZU19, akár 40 A-t is fogyaszthatnak, ráadásul több tápfeszültségsínre is szükség van az olyan részáramkörök számára, mint például az a videokodek, ami a Zynq EV-sorozatú eszközökbe van integrálva. Ezen belül a magfeszültségnek a névleges értéktől nem szabad 3%-nál jobban eltérnie még akkor sem, ha a terhelés a maximális érték kétharmadáról a teljes terhelésre ugrik. Ez egy ZU19-eszköznél 25 A-ről 40 A-re történő terhelésugrást jelent.

A Zynq UltraScale+ eszközök a felhasználói I/O-csatlakozópontokon SerDes egységeket is tartalmaznak, amelyek révén – nagy sebességű soros protokollal a csipen kívüli párhuzamos buszok felé – hatékonyabban manipulálhatók a SoC belső IP[2]-blokkjai és logikai áramkörei. Ezek a SerDes-blokkok használaton kívül maradnak, ha nincs rájuk szükség, de ha aktiválják azokat, további tápsínek használatát teszik szükségessé.

Ezeknél még szigorúbbak a terhelésugrásra adott válasz követelményei: a SerDes adóvevő-áramkörök akár 20 W-ot is fogyaszthatnak, az alkalmazott egységek számától és típusától függően. Ezek akár 1,5…80 Gbit/s sávszélességgel is működhetnek, miközben a tápfeszültséglengések amplitúdója nem haladhatja meg a 10 mV-ot.

Ha ezeknek a követelményeknek a teljesítése önmagában nem jelentene elég kihívást, rugalmas szervezhetőségre is szükség van, amellyel a rendszer alkalmazkodni képes a változó követelményekhez, amelyeket a projekt előrehaladása vagy az igényként felmerülő szolgáltatások bővülése okoz. Ha például a tervezés során SoC-típusváltás történik, a szükséges tápsínek száma és a felvett teljesítmény is változhat a kiválasztott típustól és a benne felhasznált erőforrások arányától függően. Emellett a tápellátó áramkörnek kis méretűnek is kell lennie, hogy megtartsa azt az előnyt a méretek terén is, amelyet a feladatnak egyetlen rendszercsipbe integrálásától várhatunk.

Az Avnet két Infineon IRPS5401 tápfeszültség-menedzsment IC-t (Power Management IC – PMIC) foglal magában az UltraZED-EG SOM tápellátásához. Mindegyik PMIC öt DC/DC-konvertert és egy kis feszültségesésű, lineáris feszültségszabályozót (LDO) tartalmaz (2. ábra). Ahhoz, hogy tovább fokozzák a megoldás rugalmasságát, a nagy – akár 40 A-t is elérő – áramfelvételű magfeszültség-tápsínek egyikét egy PWM-kimenettel is ellátták, amely olyan külső teljesítménykapcsoló-fokozat IC-t is képes vezérelni, mint a TDA21240.

Ahhoz, hogy a mérnökök valóban „repülőrajttal” foghassanak hozzá a tápellátás tervezéséhez, az Infineon 12 féle, közvetlenül felhasználható tápellátási elrendezést dolgozott ki – kifejezetten a Zynq UltraScale+ eszközökhöz. Ezek a megoldások azonban nem csak a különböző Zynq-családtagok tápellátási igényeit hivatottak kielégíteni, hanem kiszolgálják az állandóan bekapcsolt vagy energiatakarékos üzemmódokat is a SerDes aktivált vagy passzív állapotaival együtt. Más hasonló, gyakran előforduló tervezési feladatokhoz az Infineon elkészített egy „Power Cookbook” című megoldási „receptgyűjteményt”, amely minden információt a tervezőmérnökök rendelkezésére bocsát, amellyel azonosíthatják a feladatuknak megfelelő tápellátási megoldást, és egybefoglalják az összes tervezési információt azok megvalósításához, beleértve az elvi kapcsolási rajzot és a NyÁK kivitelezéséhez szükséges technológiai (gerber) fájlokat is. A 3. ábra egy szemelvényt mutat a Power Cookbook megoldásaiból, amely két PMIC áramkört használ a tápsínek teljes választékának kiszolgálására, beleértve a Zynq UltraScale+ MPSoC SerDes blokkjait is.

3. ábra Az IRPS5401 magas fokon integrált megoldást kínál a Zynq-termékcsalád tápellátási szegmensei és a SerDes-blokkok részére

Az IRPS5401 PMIC ugyancsak egyszerűsíti a tápfeszültségek helyes sorrendjét a be- és kikapcsolási folyamat során. Míg ezt komoly kihívás a felépítés saját tulajdonságaiból eredő módon megvalósítani, az IRPS5401 áramkört gyorsan lehet programozni az Infineon PowIRCenter grafikus felhasználói interfésze (Graphics User Interface – GUI) segítségével. A be- és kikapcsolási utasítás utáni késleltetéseket és a fel- és lefutási időket minden sínre külön lehet programozni azáltal, hogy a kívánt késleltetési értékeket egyszerűen beírjuk a GUI kezelőfelület rovataiba (4. ábra).

4. ábra A kívánt tápfeszültségkapcsolási sorrend megadható a PowIRCenter GUI kezelőfelületén

Az IRPS5401 tápfeszültség be- és kikapcsolási sorrendjét sokkal könnyebben és gyorsabban lehet így meghatározni, mintha minden tápsínhez saját időzítő áramkört építenénk a kapcsolási késleltetések meghatározására egy egymástól függetlenül működő csatornákra osztott tápegységtervezési megközelítéshez. Mivel a sorrendi vezérlés a PMIC beépített tulajdonsága, nincs szükség külső mikrovezérlőre vagy külön sorrendvezérlő időzítőelemek beépítésére. Ezáltal csökken a szükséges NyÁK-terület és az alkatrészköltség. Az IRPS5401 PMIC ezenkívül regisztereket és integrált analóg áramköri megoldásokat is tartalmaz a feszültségek tűréshatárainak megadására, amelyet így ugyancsak további alkatrészek beépítése nélkül valósíthatnak meg. A mérnöknek a megfelelő határok specifikálása és a tápfeszültségek helyes értékének tesztelése egyaránt megvalósítható a PowIRCenter GUI segítségével. A PowIRCenter ugyancsak alkalmas a teljes SoC-kártya tápellátás-tesztelésére is, kihasználva azt az előnyt, hogy az IRPS5401 támogatja a teljes PMBus 1.2 tápfeszültségmonitorozó utasításkészletet. Ez nagy mértékben egyszerűsíti a tápellátás megvalósításáért felelős mérnök munkáját a kész áramkör első beindítása során azzal, hogy méri a be- és kimeneti teljesítményt, a kimeneti feszültségeket, figyeli a túláramot, méri a hőmérsékletet és jelzi a tápellátási hibákat. A tápellátás állapota üzem közben, valós időben is ellenőrizhető a PMIC PMBus interfésze segítségével, amely alkalmas arra, hogy egy „tápellátás rendben” (Power Good) jelet állítson elő egy olyan teljes berendezés számára, mint egy videofeldolgozó szerver, de az adatok össze is gyűjthetők és a felhőbe feltölthetők további elemzések céljára.

Skálázható tápellátás a programozható rendszercsipek igényeihez

Az Infineon az IRPS5401 áramkört kimondottan az FPGA-k és programozható rendszercsipek tápellátási igényeihez tervezte, függetlenül azok gyártójától. Ez módszeres megoldási lehetőséget kínál a Zynq eszközök széles spektruma számára is, kezdve a belépő szintű ZU2-vel, egészen a nagy teljesítményű ZU19 sorozatig. Ez magában foglalja az alapkivitelű Zynq CG terméksort, amelybe kétmagos ARM Cortex-A53 processzormagot integráltak, a nagyobb teljesítőképességű Zynq EG eszközöket a négymagos Cortex-A53 alkalmazásprocesszorral és a Mali®-400 grafikus processzorral, valamint a Zynq EV termékcsaládot, amely a négymagos Cortex-A53-on és a Mali-400-on kívül egy H.264/H.265 videokodeket is tartalmaz a csipre integrálva.

Az Avnet UltraZED-EG SOM terméke, amely egy Zynq ZU03-EG eszköz köré épül, az IRPS5401 korszerű integrációjának és a flexibilitásának köszönheti kis méretét 3.5” (76,2mm) x 2” (50,8mm) és flexibilitását. Ugyanakkor a felhasználók is hasznát látják a tápellátás PowIRCenter révén elérhető finomhangolási lehetőségének, amellyel pontosan illeszthetik a tápellátás tulajdonságait a fejlesztés alatt álló projekt igényeihez. Ez a rugalmasság heteket, hónapokat takarít meg annak a „próba-szerencse” módszernek az időszükségletéhez képest, amelyre egyébként szükség lenne egy hagyományos tápegység tulajdonságainak optimalizálásához.

Az UltraZed-EG rendszermodulrólKártyaszámítógép extrával – 1 , Kártyaszámítógép, extrával – 2 és „Erőgép” (vastag) kártyaméretben cikkeinkben részletesen foglalkoztunk azokkal a demonstrációs és fejlesztőeszközökkel, amelyek a Xilinx processzoros és FPGA-logikát is tartalmazó rendszercsipjeinek alkalmazásba vételét hivatottak megkönnyíteni. A jelen cikk egy további, eddig még be nem mutatott fejlesztőmodult, az UltraZed-EG-t (nem tévesztendő össze a már bemutatott Ultra96 kártyával) említi azzal a céllal, hogy általa a tápellátás sajátos problémáit és azok megoldásait szemléltesse, ám a kártya a korábbi lapszámokban bemutatott eszközök sorához is csatlakozik. Ezért indokolt, hogy röviden ezt az eszközt is bemutassuk, nem csak mint az intellingens tápellátó rendszer egyik lehetséges terhelését, hanem mint önmagában is érdekes fejlesztőeszközt.

|

Összefoglalás

A jelenkor nagy sűrűségű FPGA és korszerű programozható SoC eszközei megkerülhetetlen trendet kényszerítenek a fejlesztőkre a nagyobb kapusűrűség és szolgáltatásintegráció területén, amely „felfelé hajtja” a tápsínek számát, valamint a sínenként folyó csúcsáram erősségét, miközben nagyobb DC pontosságot és jobb tranziens viselkedést várnak el a tápegységtől. Ahogy ezen eszközök használata egyre gyakoribbá válik, csökken a gyártmány kifejlesztésére rendelkezésre álló idő és a kártyaméret, miközben a rendszerszintű megfontolások, mint a teljesítménysűrűség, a tápfeszültségek bekapcsolásának sorrendje, a telemetria és a tápegység skálázhatósága, a feladat méreteihez való könnyű hozzáigazítás igénye egyre fontosabb követelményekké válnak. Egy mindezen elvárásoknak megfelelni képes tápegység tervezése összetett és igényes feladat, és jelentősen megnöveli a fejlesztés során megoldandó problémák mennyiségét és nehézségi fokát.

Egy konfigurálható PMIC, amelyet kimondottan az IC-k e kategóriájának tápellátására terveztek, flexibilis és skálázható megoldást kínál, amely egyebek közt az Avnet’s UltraZed-EG programozható SoC áramkörénél is megkönnyíti a Xilinx Zynq UltraScale+ MPSoC áramkörök alkalmazásfejlesztését.

Hivatkozások

[1] Xilinx UG583 UltraScale Architecture PCB Design (https://www.xilinx.com/support/documentation/user_guides/ug583-ultrascale-pcb-design.pdf)

[2] Infineon Power Solutions for Xilinx Zynq UltraScale+ MPSoC (https://www.infineon.com/dgdl/Infineon-Infineon+Scalable+Power+for+Xilinx+Zynq+UltraScale+Plus+rev0.6a-ATI-v01_00-EN.pdf?fileId=5546d46259b0420a0159d68054b10ef7)

|

Szerzők:

|

Udo Blaga – Avnet SilicaTony Ochoa – Infineon |

Avnet Silica

1117 Budapest, Budafoki út 91-93.

Barbarics Tamás

E-mail: Ez az e-mail-cím a szpemrobotok elleni védelem alatt áll. Megtekintéséhez engedélyeznie kell a JavaScript használatát.

Tel.: +36 1 436 7211

avnet-silica.com