A szabályozóhurok minőségének javítása digitális tápegységekben

A Microchip dsPIC33EP „GS”-család teljesítményelektronikai alkalmazása

A Microchip dsPIC33EP „GS”-család teljesítményelektronikai alkalmazása

A mikrovezérlők növekvő teljesítménye és bővülő perifériakínálata egyre inkább lehetőséget teremt azok valósidejű teljesítményelektronikai felhasználására. Erre mutat példát a Microchip hardver jelprocesszort is tartalmazó MCU-családját felhasználó alkalmazása, amely a digitális szabályozás optimalizálási lehetőségeire is rávilágít.

Állandóan növekszik az igény az egyre nagyobb teljesítménysűrűségű és jobb minőségű tápegységek iránt, amelyekhez a növekvő kapcsolási frekvencián keresztül vezet az út. Ez megköveteli, hogy a digitális tápegységvezérlők is alkalmazkodjanak a piaci trend által megkövetelt igényszinthez. Ennek jellemző példája a Microchip dsPIC33EP „GS”-sorozatú digitális jelvezérlők (DSC[1]-k) alkalmazása a tápegységekben. Ezek az eszközök olyan új képességekkel rendelkeznek, amelyek gyorsítják például egy lineáris differenciaegyenlet (LDE) megoldását, a teljes rendszer késleltetési idejét is csökkentve ezzel. Ezek a képességek a vezérlőhurokban alkalmazott mintavételezést magasabb frekvenciával teszik lehetővé, ezenkívül pedig mérséklik a fázistartalék csökkenését, növelve ezzel a hurokerősítés minőségi jellemzőit.

Egy digitális tápegységben[2] (PSU) van néhány olyan tényező, amely a mikrovezérlőtől teszi függővé a szabályozóhurok paramétereit. Ezek közé tartozik a maximális mintavételi frekvencia, a kompenzálóalgoritmus futásideje, az analóg/digitális átalakítók (ADC) mintavételi és konverziós ideje és a mikrovezérlő működési sebessége. A csúcsáram-szabályozáson alapuló teljesít-ményátalakítókban a komparátor sebessége, valamint a digitál/analóg átalakítók (DAC) pontossága és sebessége is hatást gyakorol a PSU hurokerősítés-tulajdonságaira. Emiatt tehát mindezeket az alkatrész-tulajdonságokat figyelembe kell venni, amikor egy adott alkalmazáshoz mikrovezérlőt (MCU) választunk.

Az új dsPIC33EP MCU legfigyelemreméltóbb tulajdonsága a nagyobb működési frekvencia. Ez most már 70 MHz, amellyel az eszköz 20 millió utasítás/s-al (MIPS) haladja meg a létező dsPIC33FJ-eszközök teljesítőképességét. Ha példaként vesszük, hogy egy ciklus ismétlődési frekvenciája 250 kHz, és egy ciklus lefutása közben 60 utasítás hajtódik végre, ez 15 MIPS számítási teljesítményt jelent, amely egy dsPIC33FJ mikrovezérlő erőforrásainak 30%-a. Ugyanez a vezérlőhurok az új dsPIC33EP processzor erőforrásainak csupán 20%-át köti le, ha ugyanazzal a ciklusismétlési (mintavételi) frekvenciával futtatjuk. Ha viszont ugyanakkora erőforrás-igénybevételt engedünk meg a dsPIC33EP-eszközökön, a szabályozóhurok mintavételi frekvenciáját 350 kHz-re növelhetjük. További vizsgálattal kimutatható az is, hogy egy adott törésponti frekvenciánál 29%-kal kisebb a fázistartalék romlása. Az 1. képlet a fázistartalék változását mutatja a törésponti frekvencia függvényében:

1. képlet A mintavételezés miatti fázistartalék-csökkenés

A legtöbb, digitális kompenzátort tartalmazó tápegységnél a teljesítményfokozat vezérlési algoritmusának alapja tipikusan egy egyszerű lineáris differenciaegyenlet[3] (LDE). Ez a matematikai megközelítés jól ismert és általánosan használt, bár bizonyos digitális szabályozási megvalósításoknál gyakran alkalmaznak nemlineáris szabályozási algoritmusokat. Ez utóbbiak tárgyalása túlmegy a jelen cikk keretein.

Az LDE „mérete” egyrészt attól függ, hányadrendű kompenzációt kívánunk megvalósítani, valamint attól a módszertől, amellyel a folytonos frekvenciafüggvényt alakítjuk át a diszkrét frekvenciatartományba (Euler-transzformáció és visszatranszformálás, bilineáris transzformáció stb.). Egyszerűen szólva az LDE egy olyan matematikai összefüggés, amely az aktuális szabályozási ciklus kimenetét a szabályozási hibák és az előző szabályozóciklus kimenete lineáris kombinációjaként állítja elő. A 2. képlet egy 3 pólust és 3 zérushelyet tartalmazó lineáris differenciaegyenlet (3P3Z) egy példája:

2. képlet 3 pólusú, 3 zérushelyű (3P3Z) lineáris differenciaegyenlet

Látható, hogy a 3P3Z kompenzátor aktuális értékének számításához hét szorzásra és hét összeadásra van szükség. Ez a fajta algoritmus a dsPIC33-eszközökkel jól végrehajtható. Ezek a műveletek hét, egyenként egy órajelciklus alatt végrehajtódó MAC (Multiply and Accumulate – szorzás és összegzés) utasítással elvégezhetők. Ellenben van néhány elkerülhetetlen, járulékos szoftverművelet (overhead), mint a munkaregiszterek verembe (stack) betároló (push) és az abból visszaállító (pop) műveletei, a munkaregiszterek írása és olvasása, tömbök feltöltése alapértelmezett értékekkel, továbbá a kimeneti értékek határolása és skálázása. Ez az overhead ugyancsak csökkent(het)i a vezérlőhurok lehetséges maximális végrehajtási gyakoriságát, amely a fázistartalék csökkenésében nyilvánulhat meg.

Amint korábban láthattuk, a MIPS-érték növekedtével valamelyest csökken a szabályozóhurok ciklusmagjának végrehajtási ideje. Még jelentősebb javulás érhető el azonban azzal, hogy az új dsPIC33EP „GS” eszközökben további alternatív munkaregiszter-készletek is megtalálhatók. Ez a 15 munkaregiszterből álló regiszterkészlet két újabb példányát jelenti, amelyben állandóan használt adatokat lehet a leggyorsabb elérhetőségű tárolóhelyen tartani. Ez azt jelenti, hogy a vágási szintek, a skálatényezők, az együtthatók gyors címzésére szolgáló memóriamutatók (pointerek) stb. az eszköz programfutás-inicializálási fázisában betölthetők az alternatív munkaregiszterekbe. Ezeket a regiszterkészleteket aztán adott programmegszakítás-prioritási szintekhez lehet hozzárendelni, amelyekhez így csak a szabályozóhurkot megvalósító szoftver férhet hozzá. Ez feleslegessé teszi, hogy a munkaregisztereket veremben tároljuk, és csökkenti azt az overhead-et azáltal, hogy a munkaregiszterekből kell (gyors hozzáféréssel) elővenni a kompenzátor-algoritmus végrehajtásához szükséges adatokat.

A 3. ábra példát mutat arra, hogyan kell inicializálni egy alternatív munkaregiszter-készletet, hogy kihasználhassuk a Microchip új processzorának hardvergyorsító funkcióit a kompenzátorprogram futtatása közben. Fontos emlékeznünk arra, hogy bizonyos regiszterek kimondottan bizonyos utasításokhoz kötődnek, amely korlátozza az adatok tárolási helyének megválasztását.

A 3. ábra példát mutat arra, hogyan kell inicializálni egy alternatív munkaregiszter-készletet, hogy kihasználhassuk a Microchip új processzorának hardvergyorsító funkcióit a kompenzátorprogram futtatása közben. Fontos emlékeznünk arra, hogy bizonyos regiszterek kimondottan bizonyos utasításokhoz kötődnek, amely korlátozza az adatok tárolási helyének megválasztását.

Vizsgáljuk meg közelebbről, hogyan befolyásolja az alternatív regiszterkészlet a nagyfrekvenciás szabályozóhurok programjának számítási teljesítményigényét („MIPS-fogyasztását”). Ha egy kompenzátor-algoritmust végrehajtó programrészletet, amelyet a dsPIC33FJ minden kapcsolási ciklusában meghívunk, az mindig a processzor MIPS-teljesítményének ugyanakkora hányadát veszi igénybe. A fázistartalék „eróziójának” mértékét az 1. képletben láthattuk. A fázistartalék leromlásának mértéke a törésponti frekvenciától és a mintavételi frekvenciától függ. Következésképpen, ha a mintavételi gyakoriságot megkétszerezzük, a fázistartalék degradációja a felére csökken. Ez azt jelenti, hogy a fázistartalék romlása, ami 29%-ot csökkent a processzorteljesítmény növekedése következtében, akár 50%-ot is gyorsulhat az alternatív munkaregiszter-készletek alkalmazása következtében.

Hogy szemléltessük a fázistartalék romlásának csökkenését a mintavételi frekvencia növekedése következtében, vegyünk példának egy rendszert, amelynek 175 kHz a mintavételi frekvenciája, és 10 kHz a sávszélessége. A fázistartalék ennek következtében – durva számítás szerint – 10 fokkal romlik. Ha ugyanezt a rendszert 350 kHz mintavételi frekvenciával használjuk, a fázistartalék degradációja csak 5°. Ezt a fázistartalék-többletet tehát azzal értük el, hogy a dsPIC33EP-eszközön használtunk fel ugyanannyi MIPS számítási teljesítményt, mint a dsPIC33FJ-n.

Kimutattuk tehát, hogy csupán az alternatív regiszterkészlet célszerű használatával és a dsPIC33EP-eszközök gyorsabb működésével magasabb mintavételi frekvenciát érhetünk el, aminek következtében a fázistartalék leromlása csökkent. A továbbiakban vizsgáljuk meg azt is, milyen mértékben javíthatja a fázistartalékot, illetve ennek következtében a hurokerősítés minőségét az alkatrész-specifikus perifériák és módszerek használata.

A dsPIC33EP „GS” eszközcsalád új típusú, 12 bites AD-kon-vertert tartalmaz, amely többmagos, szukcesszív, approximációs (SAR) konverziós eljárást alkalmaz. Az eszköz több analóg bemenet szimultán mintavételezését teszi lehetővé, és az egyes 12 bites felbontású mérési eredmények 300 ns-on belül rendelkezésre állnak. Az egyes bemenetekhez rendelt SAR-magok folyamatosan követik a bemeneti jel változását, ami azt jelenti, hogy magának a mintavételezésnek nincs külön időszükséglete.Amikor az AD-konverter egy trigger-eseményt észlel, az automatikusan elindítja a konverzió folyamatát. Ha arra gondolunk, hogy a mintavételi és konverziós időt a szabályozóhurok késleltetéseként kell figyelembe venni, a teljes mintavételi és konverziós latenciaidő minimalizálása hozzájárul a fázistartalék elkerülhetetlen romlásának csökkenéséhez.

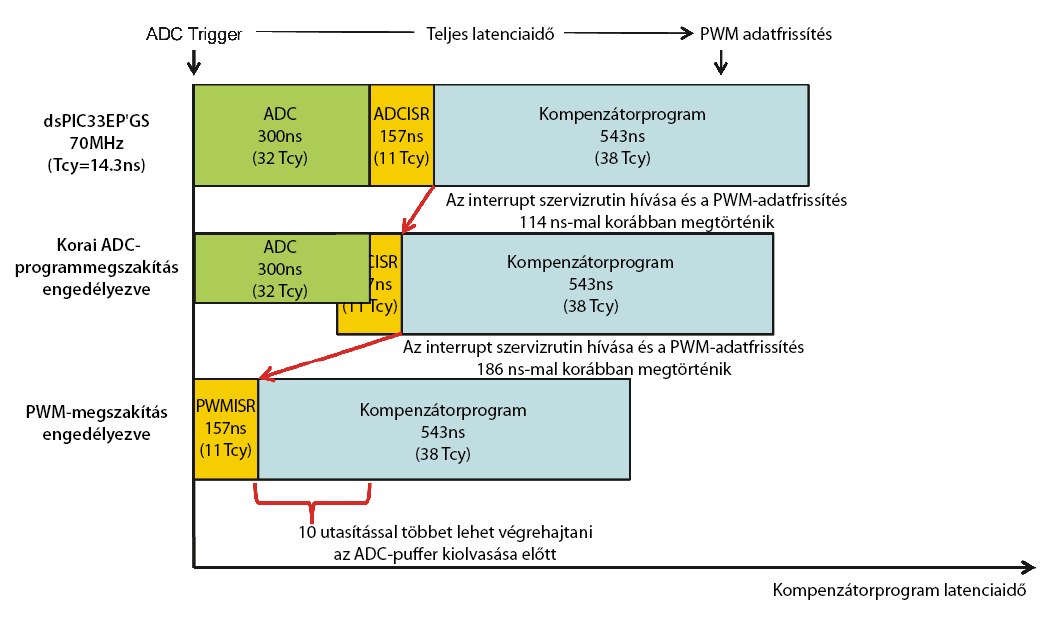

Az AD-konverter egyedülálló tulajdonsága, hogy már a konverziós folyamat végetérte előtt képes programmegszakítást generálni. Ha engedélyezzük ennek a „korai megszakítási” képességnek az érvényesülését, ez is hozzájárul annak az időnek a csökkentéséhez, ami az AD-konverzió befejezése és a vezérlőhurok szoftverének (a megszakításkiszolgálásnak) az elindítása között eltelik. A maximális kiválasztható korai megszakítási időzítés nyolc órajelciklusnyi idő (Tads). Ez a kompenzátoralgoritmus futásidejének akár 114 ns-mal való csökkentését is eredményezheti. Ez ismét csak egy újabb lehetőség a vezérlőhurok-szoftver latenciaidejének csökkentésére. A 4. ábra az AD-konverter korai megszakítási képességével elérhető időnyereséget szemlélteti.

Az ADC-modul egy másik hasznos tulajdonsága a digitális komparátoroknak az a készlete, amelyek úgy konfigurálhatók, hogy megszakítást adjanak, ha a digitalizált analóg mérési eredmény kívül (vagy belül) van a korlátozásoknak egy bizonyos kombinációján. Ez látszólag nem olyan képesség, ami közvetlen hatást gyakorolna a szabályozóhurok mintavételi frekvenciájára, de a valóságban nagyon is alkalmas erre. Kevesebb MIPS-ben kifejezhető számítási kapacitás használódik fel ugyanis, ha a CPU-t tehermentesítjük a szoftveres határellenőrzés feladatától a digitális komparátorok által elvégzett határérték-ellenőrzés által. Emiatt a processzornak csak határérték-túllépés esetén kell szoftvervégrehajtással beavatkoznia. Ez viszont azt jelenti, hogy megnövelhetjük a szabályozóhurok mintavételi frekvenciáját. Mindez természetesen nagymértékben szoftverfüggő, azaz nem minden alkalmazás képes kihasználni ennek az új tulajdonságnak az előnyeit. Ugyanakkor ezzel a képességgel csökkenthetjük a CPU munkaterhelését, és a felszabaduló számítási teljesítménnyel például a bemeneti feszültség és a hőmérséklet folytonos felügyeletének a feladatát is elláthatjuk.

Annak érdekében, hogy még tovább csökkenthessük azt az időt, amely az AD-konverter triggerjelének kiadásától a szabályozóhurok kimeneti értékének visszaírásáig eltelik, célszerű az impulzusszélesség-modulátor (PWM) megszakításkiszolgáló rutinját (Interrupt Service Routine – ISR) használni az ADC ISR-je és az ADC – már említett – korai megszakítási lehetősége helyett. Általában a PWM adja a triggerjelet az ADC konverziós folyamatának elindításához, de itt egyidejűleg egy saját programmegszakítási eseményt is generál. Azzal, hogy a kompenzátor-algoritmust a PWM ISR-be építjük be, a szoftver már azt megelőzően elkezdhet végrehajtódni, hogy a visszacsatolt jelből vett aktuális minta digitalizált értéke rendelkezésre állna az ADC kimenetén. Nagyjából 143 ns áll rendelkezésre a megszakítási rutin futásának kezdetétől az AD-konverzió befejeződéséig. Ez azt jelenti, hogy – ha a mikrovezérlő a maximális órafrekvenciájával fut – legalább 10 utasítást végrehajthatunk, mielőtt az AD-konverter kimeneti puffertárolójában megjelenne a mérési eredmény. Ha a kompen-zátoralgoritmust olyan módon építjük fel, hogy „előre dolgozunk”, és kihasználjuk ezt a 10 utasításnyi processzoridőt, ez akár 45%-kal is csökkentheti a kompenzátorprogram végrehajtási idejét. A 4. ábrát már felhasználtuk a „korai megszakításos” alkalmazási példa szemléltetésére, de az ábra a PWM ISR-be épített kompenzátorrutinnal felépített megoldással való összehasonlításra is lehetőséget ad. Fontos megjegyezni azonban, hogy ez a módszer csak akkor alkalmazható, ha előre tudhatjuk az AD-konverter konverziós idejét. Ez a feltétel a vizsgált DSC SAR-elvű AD-konvertereinél teljesül.

4. ábra Az AD-konverter korai megszakítási funkciójának időzítése

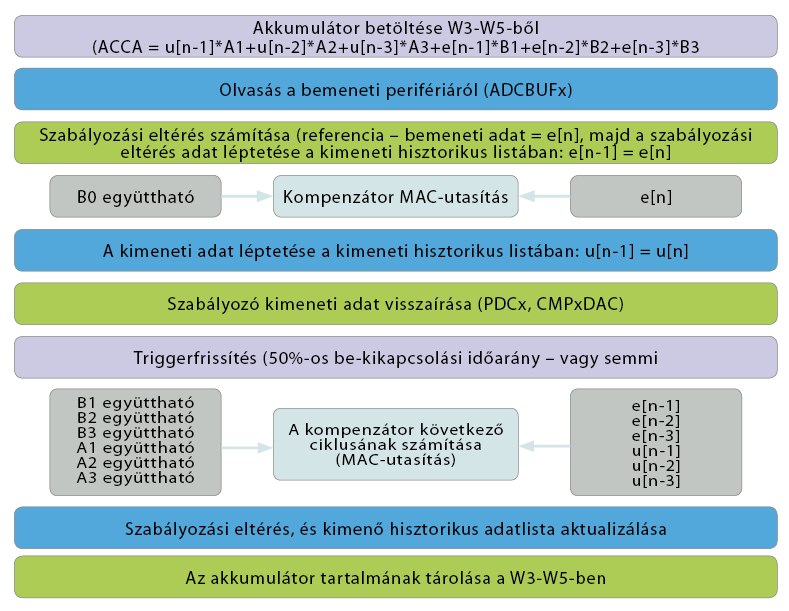

A kompenzátoralgoritmus szerkezeti felépítésének tehát fontos szerepe van annak az időtartamnak a meghatározásában, ami ahhoz szükséges, hogy a szabályozóalgoritmus kimeneti változójában megjelenjen az aktualizált érték. A már említett alternatív munkaregiszter-készlettel az algoritmus megírható úgy, hogy az egyetlen szükséges számítás, ami a vezérlőkimenet előállításához szükséges, csupán abból áll, hogy az aktuális szabályozási eltérést megszorozzuk egy B0 együtthatóval, és az eredményt hozzáadjuk az előző ciklus során már akkumulált kimeneti adathoz. Természetesen a kimeneti érték normalizálásához és az érték határolásához már elvégzett műveleteket „vissza kell csinálni” – de még így is jelentősen csökkenthető a szabályozóhurok kimeneti értékének előállításához szükséges idő. Az 5. ábra példát mutat arra, hogyan lehet megfogalmazni a kompenzátoralgoritmust úgy, hogy elérje a kimenet frissítéséhez szükséges, lehető legrövidebb időt. A kompenzátorrutinba történő belépéstől a szabályozókimenet új értékének beírásáig eltelő idő ezzel a módszerrel akár 300 ns-nál kevesebb is lehet. Hogy ennek az előnyét hogyan lehet kihasználni, az a következő fejezetben világossá válik.

5. ábra Egy hardverrel segített 3P3Z-kompenzátor tömbvázlata

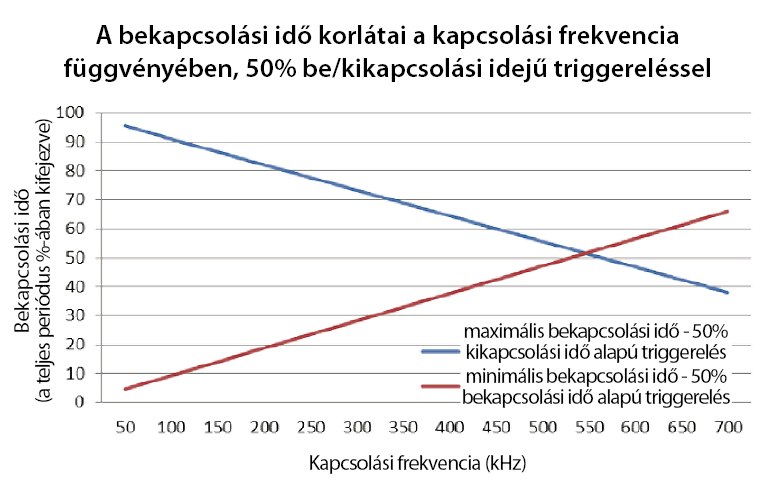

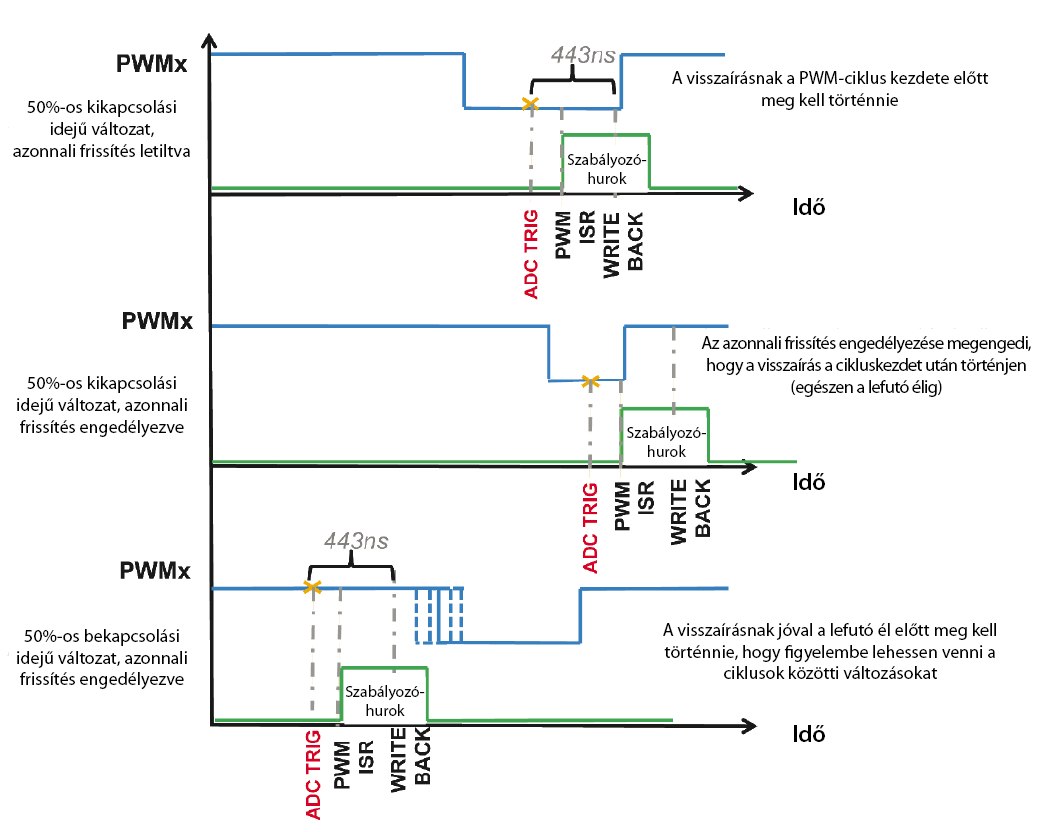

Most vizsgáljuk meg, milyen hatással vannak a fázistartalék romlására együttesen azok a különféle tulajdonságok, amelyeket eddig áttekintettünk. A feszültség-üzemmódú és az átlagáram-üzemmódú szabályozásoknál lehetőség van arra, hogy a kimeneti kondenzátor feszültségét vagy az induktivitáson folyó áramot mintavételezzük az 50%-nyi kikapcsolási idő alatt. A legjellemzőbb megközelítés az, hogy az 50%-nyi bekapcsolási idő alatt mintavételezünk, hogy elég időt hagyjunk a szabályozóalgoritmus végrehajtására, mielőtt a következő PWM-ciklus elkezdődne. Az előbbiekben említett összes gyorsítási képességet felhasználva könnyen megoldható a szabályozókör visszacsatoló jelének mintavételezése a kikapcsolási idő alatt, és a szabályozó kimeneti jelét visszaírhatjuk még a következő PWM-ciklus kezdete előtt. A 6. ábra mutatja egy mintakészüléknél a kitöltési tényező becsült határértékeit a kapcsolási frekvencia függvényében, a 7. ábra pedig az 50%-nyi kikapcsolási szakasz időzítését. A fázistartalék növekedése függ ugyan a kitöltési tényezőtől, de ha az átlagos 50%-os kitöltési tényezővel számolunk, a fázistartalék romlása a felére csökken az 50%-os bekapcsolási időnél végzett mérés eredményéhez képest.

6. ábra A minimális és maximális bekapcsolási idő mértéke különféle triggerelési megoldásoknál

A dsPIC33EP „GS”-eszközök képesek egy azonnali frissítési (immediate update) üzemmódra is. Ha ezt engedélyezzük, akkor a processzor még az aktuális ciklusban frissíti a PWM paramétereit, és egyidejűleg írja a speciális funkcióregisztert (Special Funcion Register – SFR). Ezzel egyszerre aktualizálja a fázisszöget, a periódusidőt, a holtidőt és a kitöltési tényezőt – és mindent 1 ns felbontással. Amikor az 50%-os kikapcsolási idejű „forgatókönyvet” ismertettük, említettük, hogy a vezérlő kimenetének visszaírása meg kell hogy történjen, mielőtt az új PWM-ciklus elkezdődik, és ez határozza meg, mekkora lehet a maximális bekapcsolási idő egy adott kapcsolási frekvenciánál. Ha viszont engedélyezzük az azonnali frissítést, ez már nem így van. Ez a képesség még tovább növeli a kitöltési tényező és a kapcsolási frekvencia kihasználható tartományát, amely ismét csak segít abban, hogy minél kisebbre „faragjuk le” a fázistartaléknak a program futási ideje miatti veszteségét. A 7. ábra mutatja az 50%-os kikapcsolási idejű forgatókönyv lehetséges változatainak idődiagramját.

A legkedvezőbb eset a fázistartalék romlásának csökkentése szempontjából az 50%-os bekapcsolási idejű változat, amennyiben garantáljuk, hogy az aktuális szabályozóciklus kimenete az aktuális PWM-ciklus felfutó éle előtt érvényesítve legyen. Ez azt is maga után vonja, hogy a PWM-ciklus aktív élének megjelenése annak a kompenzátorrutinnak a kimeneti értéke szerint frissül, amelynek a hívása ugyanazon PWM-ciklus alatt történt.

7. ábra Az 50%-os kikapcsolási idejű működésmód változatainak idődiagramja

Ez adja egy digitálisan szabályozott tápegységnél az elérhető legjobb fázistartalékot. Azt azonban meg kell jegyeznünk, hogy ez csak optimális esetben van így, amely nem minden alkalmazásban valósítható meg a minimális bekapcsolási időre vonatkozó korlátozások miatt. Visszautalunk a 6. ábrára, amely a minimális bekapcsolási időt a kapcsolási periódusidőre vonatkoztatva, százalékban adja meg a kapcsolási frekvencia függvényében. Ha egy 100 kHz-es kapcsolási frekvenciájú feszültségnövelő teljesítménytényező-korrektort (Power Factor Corrector – PFC) veszünk példaként, a minimális bekapcsolási időre vonatkozó követelmény a teljes periódusidő 10%-a. A minimális kitöltési tényező, a bemeneti (névlegesen 230 V-os) váltakozó feszültség csúcsértékénél következik be. Ilyenkor a kitöltési tényező kb. 22%, amely bőségesen elég ahhoz, hogy az azonnali frissítés még a szabályozókimenet értékének jelentős változásai esetén is végrehajtódhasson. Amint a bemeneti feszültség tovább növekszik, az azonnali frissítés egyre közelebb kerül a szabályozási ciklus végén történő adatfrissítéshez, amely miatt csökken a fázistartalék. Ez viszont a névleges működési tartományán kívül történik csak meg. A 7. ábra egy 50%-os bekapcsolási idejű triggerelési séma idődiagramját is bemutatja, amely ezt szemlélteti.

Megépítettünk egy szinkron feszültségcsökkentő mintaáramkört az összes felsorolt technikák felhasználásával. Az eredmények azt mutatják, hogy ezekkel a szabályozás mintavételi frekvenciája a minden második PWM-ciklusban történő mintavételről (175 kHz) minden egyes PWM-ciklusban történő mintavételre (350 kHz) volt növelhető anélkül, hogy ehhez több MIPS számítási teljesítmény igénybevételére lett volna szükség. A kompenzátoralgoritmust úgy írtuk meg, hogy a szabályozó kimeneti változójának gyors visszaírása valósuljon meg, a PWM-megszakítást alkalmaztuk a szabályozóprogram futásának indítására, az 50%-os bekapcsolási idejű sémát alkalmazzuk és engedélyeztük az azonnali frissítést. Azt figyeltük meg, hogy a fázistartalék nagyjából 16 fokkal növekedett. A hurokerősítés csak 46 foknál lépett a feltételesen stabil állapotba, és egy olyan értékig (62°) tartott, amely már az analóg szabályozási hurkokra jellemző. A fázistartalék csökkenésének megakadályozására az e cikkben felsorolt módszerek nem oldanak meg minden problémát, viszont az ötletek számos áramköri tervnél használhatók, és a digitális szabályozóhurok minőségi jellemzőinek bizonyos fokú javulását eredményezhetik.

[1] A valósidejű digitális jelfeldolgozás tipikus feladata a szorzatok összegzésén alapuló algoritmusok ( például Fast Fourier Transform (FFT) és más jeltranszformációk) végrehajtása. Az erre szolgáló céláramköröket nevezik digitális jelfeldolgozó processzornak (Digital Signal Processor – DSP). A DSP-funkcióra (is) képes, de a mikrovezérlőkhöz hasonlóan célperifériákkal, esetleg hagyományos mikroprocesszormaggal is kiegészített áramköreit nevezi a Microchip „digitális jelvezérlőnek” (Digital Signal Controller – DSC). – A ford. megj.

[2] A cikk ismertnek tételezi fel a digitális (értsd: digitális szabályozással működő) tápegységek működését és tömbvázlatát, és ez bizonyára számos olvasónk számára ismert is. Az olvashatóság és a használt fogalmak egységes értelmezése érdekében azonban mégis hasznos összefoglalni, mit is értenek ezen. A „digitális tápegység” olyan kapcsolóüzemű tápegység, amelynek feszültség- és/vagy áramszabályozását a szabályozott jellemző AD-konverterrel történő periodikus mintavételezése alapján, egy mikrovezérlő által kiszámított beavatkozójellel végezzük. Azt az egységet, amely a szabályozott jellemzőből előállítja a beavatkozójelet, a cikk „kompenzátornak” nevezi, mivel az analóg szabályozóhurkok frekvenciakompenzációjának megfelelő feladatot látja el digitális, numerikus módszerekkel. A kompenzátor frekvenciafüggésének módjától függ a szabályozott tápegység stabilitása, amelynek a biztos működés érdekében egy bizonyos fázistartalékkal kell rendelkeznie. A fázistartalék mértékét a kompenzátor-rutin ciklusmagjának futási ideje korlátozza. Minél hosszabb ez a futási idő, annál nagyobb mértékben romlik a fázistartalék, és annál kisebb behatás is képes a tápegységet a stabil működésből kibillenteni. A cikk arra keresi a választ, milyen hardvereszközökkel és szoftverarchitektúrákkal lehet a ciklusmag futási idejét (és ezzel a számítógéppel szimulált szabályozóhurok késleltetését) csökkenteni, azaz hogyan lehet minél többet megőrizni az adott pólus-zérus elrendezésű szabályozóalgoritmus által meghatározott elméleti fázistartalékból. – A szerk. megj

[3] A lineáris differenciaegyenlet a matematikai analízisben megszokott, infinitezimális különbségeken alapuló lineáris differenciálegyenletek véges differenciákkal felírt, numerikus számításra alkalmas változata – A ford. megj.